# НАУКОВІ ПРАЦІ ДОНЕЦЬКОГО НАЦІОНАЛЬНОГО ТЕХНІЧНОГО УНІВЕРСИТЕТУ

# Серія: «Проблеми моделювання та автоматизації проектування»

Nº 1(12)-2(13)`2013

Донецьк - 2013

### МІНІСТЕРСТВО ОСВІТИ І НАУКИ УКРАЇНИ

## НАУКОВІ ПРАЦІ

### ДОНЕЦЬКОГО НАЦІОНАЛЬНОГО ТЕХНІЧНОГО УНІВЕРСИТЕТУ

# Серія «Проблеми моделювання та автоматизації проектування»

Випуск присвячується 40-річчю співробітництва ДонНТУ і Штутгартського університету в галузях моделювання, САПР, автоматизації динамічних систем, паралельних і розподілених обчислень.

Всеукраїнський науковий збірник

Заснований у червні 1999 року

Виходить 2 рази на рік

№ 1(12)-2(13)`2013

Донецьк - 2013

#### УДК 62-50+681.3(06)

Публікується згідно з рішенням Вченої ради державного вищого навчального закладу «Донецький національний технічний університет», протокол № 4 від 18.04.2014

У збірнику опубліковано статті співробітників факультету комп'ютерних наук та технологій, а також — інших факультетів ДонНТУ. В публікаціях наведено результати наукових досліджень та розробок, виконаних у 2012—2013 роках в наступних напрямках: теоретичні аспекти моделювання та автоматизації проектування, методи та засоби моделювання, методи та засоби автоматизації проектування, спеціалізовані обчислювальні системи моделювання, контроль процесів та керування динамічними системами. До збірки включено також публікації співробітників інших університетів та організацій, які  $\epsilon$  науковими партнерами ДонНТУ і активно співпрацюють у спільних дослідженнях. Матеріали збірки призначені для викладачів, наукових співробітників, інженерно-технічних працівників, аспірантів та студентів, що займаються питаннями дослідження, моделювання та розробки складних динамічних систем.

Засновник та видавець - Донецький національний технічний університет

#### РЕДАКЦІЙНА КОЛЕГІЯ

Чл.- кор. НАН України, д-р техн. наук, проф. О.А. Мінаєв (головний редактор), д-р техн. наук, проф. Є.О. Башков (заст. головного редактора), д-р техн. наук, проф. В.А. Святний (заст. головного редактора, відп. за випуск), канд. техн. наук, проф. О.Я. Анопрієнко (відп. секретар випуску), д-р фіз.-мат. наук, проф. А.С. Барашко, д-р техн. наук, проф. О.О. Баркалов, д-р техн. наук, проф. Н.М. Куссуль, канд. техн. наук, проф. В.В. Лапко, д-р техн. наук, проф. Ю.О. Скобцов, д-р техн. наук, проф. Л.П. Фельдман.

Збірник зареєстрований в Державному комітеті інформаційної політики, телебачення та радіомовлення України. Свідоцтво КВ № 7377 від 03.06.2003.

Збірник включено до Переліку наукових фахових видань України, в яких можуть публікуватися результати дисертаційних робіт на здобуття наукових ступенів доктора і кандидата наук (Затверджено постановою президії ВАК України від 10.11.2010 р. № 1-05/7).

# **3MICT**

| Святний В.А. 40 років наукового співробітництва Донецького національного технічного університету з Штутгартським університетом (Німеччина)                                  | 5   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Аноприенко А.Я. Основные закономерности эволюции компьютерных систем и сетей                                                                                                | 10  |

| Баркалов А.А., Титаренко Л.А., Ефименко К.Н., Зеленёва И.Я. Реализация КМУУ с общей памятью на гибридных FPGA                                                               | 33  |

| Belovodskiy V.N., Sukhorukov M.Y., Bukin S.L. To the question of forming biharmonic oscillations in two masses nonlinear vibrating machines under ideal harmonic excitation | 43  |

| Криводубский О.А., Терещук И.В. Статистическая модель задачи бюджетирования                                                                                                 | 55  |

| Кушнаренко В.Г. Моделювання гілки мережного динамічного об'єкта з<br>зосередженими параметрами на основі блокових чисельних методів                                         | 66  |

| Назимко В.В., Кратт О.А., Мерзликин А.В. Динамическая модель для исследования проектных рисков угледобычи                                                                   | 75  |

| Ковалевский Н.А., Приходько Т.А. Разработка протокола для мобильных сетей и исследование его в среде Network Simulator 2 (NS2)                                              | 87  |

| Селякова С.М. Модификация метода электра решения задач многокритериального выбора для случая переменного значения весов критериев                                           | 95  |

| Хомяк Т.В. Моделирование твердого тела с жидкостью системой связанных твердых тел                                                                                           | 101 |

| Barkalov A.A., Titarenko L.A., Tsololo S.A., Miroshkin A.N. Hardware reduction in CPLD-based moore FSM                                                                      | 110 |

| Чередникова О.Ю. Синтез замкнутой системы оптимального по быстродействию управления с ограничением регулируемой координаты                                                  | 120 |

| Шамаев В.В., Василенко А.В., Хачатурова Т.А. Моделирование работы спинового фильтра, основанного на квантовом размерном эффекте                                             | 130 |

| Иванов Ю.А., Первусяк А.И. Исследование разноинерционной модели движения токоприемника локомотива на многоядерной системе                                                   | 138 |

| Иваница С.В. Реализация арифметических операций сложения и вычитания над тетракодами                                                                                        | 149 |

| Дмитриева О.А. Параллельное моделирование на основе сведения полной матрицы многостадийного метода                                                                          | 159 |

| Беловолова М.А., Зинченко Ю.Е. Архитектура системы диагностики аналоговых устройств на базе нейронной сети и спектрального анализа                                          | 171 |

| Шевчук О.А. Статические статистические модели прогноза расходов от использования строительной техники                                                                       | 180 |

| Анопрієнко О.Я., Варзар Р. Суперсенсорный компьютинг в повышении точности метеопрогнозов                                                                                    | 189 |

| Правила представлення і оформлення публікацій                                                                                                                               | 201 |

- 33 -

УДК 004.274

**А.А. Баркалов**<sup>1,2</sup> (д-р техн. наук, проф.), **Л.А. Титаренко**<sup>1</sup> (д-р техн. наук, проф.),

**К.Н. Ефименко<sup>2</sup>** (канд. техн. наук, доц.), **И.Я. Зеленёва<sup>2</sup>** (канд. техн. наук, доц.)

Университет Зеленогурский, г. Зеленая Гура, Польша<sup>1</sup>, A.Barkalov@iie.uz.zgora.pl<sup>1</sup>

Донецкий национальный технический университет<sup>2</sup>

### РЕАЛИЗАЦИЯ КМУУ С ОБЩЕЙ ПАМЯТЬЮ НА ГИБРИДНЫХ FPGA

Предлагается метод уменьшения аппаратурных затрат в схеме КМУУ с общей памятью, ориентированный на технологию гибридных FPGA. Метод основан на использовании двух источников кодов классов псевдоэквивалентных ОЛЦ и реализации схемы адресации микрокоманд на встроенных PLA. Такой подход позволяет уменьшить общую площадь кристалла, занимаемую схемой устройства управления. Приведен пример применения предложенного метода.

Ключевые слова: КМУУ, алгоритм управления, операторная линейная цепь, гибридные FPGA, PLA, логическая схема.

### Введение

В случае, если алгоритм управления некоторой системы представлен линейной граф-схемой алгоритма (ГСА) [1], для реализации схемы (УУ) может устройства управления быть использована композиционного микропрограммного устройства управления (КМУУ) с общей памятью [2,3]. В настоящее время для реализации схем УУ широко используются программируемые логические интегральные схемы (ПЛИС) вида FPGA (field-programmable gate arrays) [4,5]. Основу FPGA представляют макроячейки LUT (look-up table), имеющие ограниченное число входов (4-6) [6,7]. Кроме того, в настоящее время развивается технология гибридных FPGA [8,9], в состав которых входят LUTэлементы, встроенные блоки памяти (EMB, embedded memory blocks) и встроенные программируемые логические матрицы (PLA, programmable logic array). При этом появляется возможность реализации части схемы на блоках PLA. Это позволяет уменьшить площадь кристалла, занимаемую схемой КМУУ. Метод основан на использовании двух источников кодов классов псевдоэквивалентных операторных линейных цепей (ОЛЦ). Предложенный метод развивает идеи из работы [10].

**Целью исследования** является оптимизация схемы КМУУ с общей памятью за счет использования возможностей, представляемых технологией гибридных FPGA.

Задачей исследования является разработка метода синтеза КМУУ с общей памятью, позволяющего уменьшить число LUT-элементов в комбинационной части КМУУ.

### Композиционное МУУ с общей памятью

Пусть ГСА  $\Gamma = \Gamma(B,E)$  представлена множествами вершин B и соединяющих их дуг E. Пусть  $B = b_0 \cup b_E \cup E_1 \cup E_2$ , где  $b_0$  — начальная вершина,  $b_E$  — конечная вершина,  $E_1$  — множество операторных вершин и  $E_2$  — множество условных вершин ГСА  $\Gamma$ . B операторных вершинах  $b_q \in E_1$  записываются наборы микроопераций  $Y(b_q) \subseteq Y$ , где  $Y = \{y_1,...,y_N\}$  — множество микроопераций. B условных вершинах  $b_q \in E_2$  записываются элементы множества логических условий  $X = \{x_1,...,x_L\}$ . Введем ряд определений, взятых из [1].

**Определение 1**. Операторной линейной цепью ГСА  $\Gamma$  называется конечная последовательность операторных вершин  $\alpha_g = \left\langle b_{g1},...,b_{gF_g} \right\rangle$  такая, что для любой пары соседних компонент  $b_{gi},b_{gi+1}$ , где i – номер компоненты кортежа  $\alpha_g$ , существует дуга  $\left\langle b_{gi},b_{gi+1} \right\rangle \in E$ .

**Определение 2**. Вершина  $b_q \in D^g$ , где  $D^g$  — множество вершин, входящих в ОЛЦ  $\alpha_g$ , называется входом ОЛЦ  $\alpha_g$ , если существует дуга  $\left\langle b_t, b_q \right\rangle \in E$ , где  $b_t \not\in D^g$ .

$\label{eq:continuity} \textit{Определение 3}. \ \ \mbox{Вершина} \ \ b_{q} \in D^{g} \ , \ \mbox{называется выходом ОЛЦ} \ \ \alpha_{g} \ ,$  если существует дуга  $\left\langle b_{q}, b_{t} \right\rangle \in E \ ,$  где  $b_{t} \not\in D^{g} \ .$

**Определение 4**. ОЛЦ  $\alpha_i, \alpha_j$  называются псевдоэквивалентными ОЛЦ, если их выходы связаны со входом одной и той же вершины  $b_q \in B$ .

Пусть для некоторой ГСА Г сформировано множество ОЛЦ  $C = \{\alpha_1, ..., \alpha_G\}$ , определяющее разбиение на множестве  $E_1$  [3], и пусть  $\left|E_1\right| = M$ . Поставим в соответствие каждой вершине  $b_q \in E_1$  микрокоманду  $MI_q$  с адресом  $A(b_q)$ , имеющим разрядность

$$R = \lceil \log_2 M \rceil. \tag{1}$$

Используем для адресации микрокоманд переменные  $T_r \in T$ , где |T| = R.

- 35

Адресация выполняется таким образом, чтобы выполнялось условие

$$A(b_{gi+1}) = A(b_{gi}) + 1,$$

(2)

где  $b_{gi}, b_{gi+1} \in D^g$  и  $\left\langle b_{gi}, b_{gi+1} \right\rangle \in E$  .

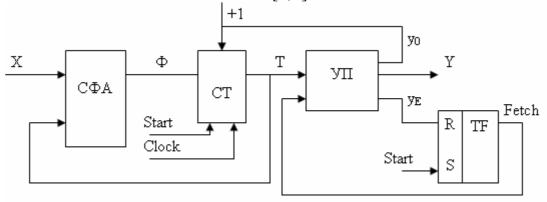

В этом случае УУ может быть реализовано в виде КМУУ  $U_1$  (рис. 1), называемом КМУУ с общей памятью [2,3].

Рисунок 1 – Структурная схема КМУУ U<sub>1</sub>

В КМУУ  $U_1$  схема формирования адреса (СФА) реализует систему функций возбуждения триггеров счетчика СТ, определяемую как

$$\Phi = \Phi(T, X). \tag{3}$$

При этом, как правило, счетчик имеет информационные входы типа D [6,7]. По сигналу Start счетчик CT устанавливается в ноль, что соответствует адресу первой микрокоманды реализуемого алгоритма. По сигналу  $y_0 = 1$  содержимое CT увеличивается на единицу, что соответствует режиму (2). Управляющая память (УП) хранит наборы микроопераций  $Y(b_q) \subseteq Y$  и переменные  $y_0$  (управление CT) и  $y_E$  (признак окончания алгоритма). Триггер считывания TF формирует сигнал Fetch, разрешающий выборку микрокоманд из УП. При достижении окончания алгоритма формируется переменная  $y_E = 1$ , что приводит к Fetch = 0 и прекращению выборки из УП.

При использовании FPGA схемы СФА, СТ и ТF реализуются на LUT, а схема УП — на встроенных блоках памяти ЕМВ. Основным недостатком КМУУ  $U_1$  является значительное число термов в системе функций (3). Это приводит к увеличению числа LUT элементов и их уровней в схеме СФА. Для устранения этого недостатка используют оптимальную адресацию микрокоманд, что приводит к КМУУ  $U_2$  [10]. Однако такая адресация не всегда возможна. Уменьшение числа термов системе (3) гарантируется в КМУУ  $U_3$ , где осуществляется преобразование адресов микрокоманд в коды классов псевдоэквивалентных ОЛЦ [2,3]. Однако это связано с введением в схему КМУУ дополнительного блока

преобразователя адресов (БПА), который потребляет некоторые ресурсы кристалла. В настоящей работе предлагается метод синтеза КМУУ, позволяющий уменьшить как число термов в системе (3), так и число LUT элементов в схемах БПА и СФА.

### Основная идея предлагаемого метода

Найдем разбиение  $\Pi_C = \{B_1,...,B_I\}$  множества ОЛЦ C на классы псевдоэквивалентных ОЛЦ. Выполним адресацию микрокоманд так, чтобы при выполнении условия (2) максимально возможное число классов  $B_i \in \Pi_C$  выражалось одним интервалом R-разрядного булева пространства. Представим разбиение  $\Pi_C$  в виде  $\Pi_C = \Pi_1 \cup \Pi_2$ , где  $\Pi_1 \cap \Pi_2 = \varnothing$ . Пусть  $B_i \in \Pi_1$ , если этот класс представляется более, чем одним интервалом пространства кодирования. Остальные классы принадлежат множеству  $\Pi_2$ .

Характерной особенностью блоков ЕМВ является фиксированное число выходов  $t_F \in \{1, 2, 4, 8, 16, 32, 64\}$ . Пусть  $V_0$  означает число ячеек ЕМВ при  $t_F = 1$ . Тогда число ячеек V при некотором фиксированном значении  $t_F$  можно определить как

$$V = \left[ V_0 / t_F \right]. \tag{4}$$

Для реализации управляющей памяти КМУУ достаточно М ячеек EMB. При этом блок будет иметь

$$t_{M} = \lceil V_{0}/M \rceil \tag{5}$$

выходов. Пусть следующее условие выполняется для некоторой ГСА  $\Gamma$  и блоки EMB используемой микросхемы FPGA

$$t_{M} > N + 3. \tag{6}$$

Закодируем классы  $B_i \in \Pi_1$  двоичными кодами  $K(B_i)$  разрядности

$$R_1 = \lceil \log_2 I_1 \rceil, \tag{7}$$

где  $I_1 = |\Pi_1|$ . Используем для кодирования переменные  $\tau_r \in \tau$ , где  $|\tau| = R_1$ . Пусть  $\Pi_1 \neq \varnothing$ ,  $\Pi_2 \neq \varnothing$  и следующее условие выполняется для EMB одновременно с условием (6):

$$t_{\rm M} < N + 3 + R_{\rm 1}.$$

(8)

Очевидно, что часть разрядов кодов  $K(B_i)$  для классов  $B_i \in \Pi_1$  может быть сформирована схемой УП. Теперь УП формирует  $R_2$  разряда кода  $K(B_i)$ , а БПА –  $R_3$  разряда:

$$R_2 = t_M - (N+3);$$

(9)

$$R_3 = R_1 - R_2. (10)$$

При этом множество  $\tau$  может быть представлено в виде  $\tau = \tau^1 \cup \tau^2$ ,

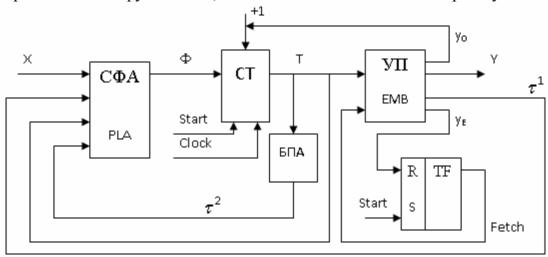

где  $\left|\tau^{1}\right|=R_{3},\;\left|\tau^{2}\right|=R_{2}$ . Предлагаемая в работе модель КМУУ основана на представлениях  $\Pi_{C}=\Pi_{1}\cup\Pi_{2}\;\;$  и  $\;\tau=\tau^{1}\cup\tau^{2}.\;$  На этих представлениях основана и модель  $U_{4}$  из работы [11]. Однако в предлагаемой структуре  $U_{5}$  схема СФА реализуется на блоках PLA (рис. 2).

Схема СФА реализует функции Ф в следующем виде:

$$\Phi = \Phi(T, \tau, X). \tag{11}$$

Блок БПА реализует часть разрядов кодов  $K(B_i)$ , образующих множество  $\tau^2$ . В отличие от КМУУ  $U_4$  [11] в схеме отсутствует мультиплексор выбора источника функций  $\Phi$ , что является несомненным преимуществом.

Рисунок 2 – Структурная схема КМУУ U<sub>5</sub>

Такой подход позволяет уменьшить число термов в системе (3) до абсолютно возможного минимума. Кроме того, уменьшается сложность блока БПА по сравнению с КМУУ  $U_3$ . Отметим, что при  $\Pi_1 = \emptyset$  КМУУ  $U_5$  вырождается в  $U_2$ . При  $\Pi_2 = \emptyset$  КМУУ  $U_5$  превращается в КМУУ  $U_3$ . Недостатком является увеличение числа выходов блока УП. Однако этот блок строится из реконфигурируемых блоков ЕМВ, которые имеют строго определенное число выходов [6,7]. При этом имеется высокая вероятность наличия неиспользованных выходов.

В настоящей работе предлагается метод синтеза КМУУ  $U_5$ , включающий следующие этапы:

- 1. Формирование множества ОЛЦ С для ГСА Г.

- 2. Формирование разбиения  $\Pi_{C}$  множества C.

- 3. Оптимальная адресация микрокоманд.

- 4. Кодирование классов  $B_i \in \Pi_1$ .

- 5. Формирование таблицы переходов КМУУ.

- 6. Формирование таблицы блока преобразователя адреса.

- 7. Формирование таблицы содержимого управляющей памяти.

- 8. Реализация схемы КМУУ в заданном элементном базисе.

### Пример применения предложенного метода

Пусть для некоторой ГСА Г получено множество ОЛЦ  $C = \{\alpha_1,...,\alpha_{12}\}$ , где  $\alpha_1 = \langle b_1,...,b_4 \rangle$ ,  $\alpha_2 = \langle b_5 \rangle$ ,  $\alpha_3 = \langle b_6,b_7 \rangle$ ,  $\alpha_4 = \langle b_8,b_9,b_{10},b_{11},b_{12} \rangle$ ,  $\alpha_5 = \langle b_{13},b_{14} \rangle$ ,  $\alpha_6 = \langle b_{15},b_{16} \rangle$ ,  $\alpha_7 = \langle b_{17},...,b_{20} \rangle$ ,  $\alpha_8 = \langle b_{21},...,b_{24} \rangle$ ,  $\alpha_9 = \langle b_{25},b_{26} \rangle$ ,  $\alpha_{10} = \langle b_{27},b_{28} \rangle$ ,  $\alpha_{11} = \langle b_{29},b_{30},b_{31} \rangle$ ,  $\alpha_{12} = \langle b_{32} \rangle$ . Пусть эти ОЛЦ могут быть разбиты на I = 7 классов, где  $B_1 = \{\alpha_1\}$ ,  $B_2 = \{\alpha_2,\alpha_3\}$ ,  $B_3 = \{\alpha_4\}$ ,  $B_4 = \{\alpha_5,\alpha_6\}$ ,  $B_5 = \{\alpha_7,\alpha_8,\alpha_9\}$ ,  $B_6 = \{\alpha_{10},\alpha_{11}\}$ ,  $B_7 = \{\alpha_{12}\}$ . Пусть выход ОЛЦ  $\alpha_{12} \in C$  связан с входом вершины  $b_E$ . Как известно, переходы из таких ОЛЦ не рассматриваются, так как их последняя вершина должна включать переменную  $y_E$  [2].

Выполним адресацию микрокоманд так, чтобы выполнялось условие (2) и максимально возможное число классов представлялось одним обобщенным интервалом R-мерного булева пространства. В рассматриваемом примере M=32, то есть R=5 и  $T=\{T_1,...,T_5\}$ . Один из возможных вариантов оптимальной адресации микрокоманд приведен на рис. 3. Этот рисунок содержит видоизмененную карту Карно, которая достаточна для получения обобщенных интервалов, соответствующих кодам классов  $B_i \in \Pi_C$ . Символ  $U_5(\Gamma)$  означает, что КМУУ  $U_5$  реализуется по  $\Gamma$ CA  $\Gamma$ .

Следующие интервалы могут быть найдены для классов  $B_i \in \Pi_C$ . Класс  $B_1$  соответствует интервалу  $000^{**}$ ; класс  $B_2$  — интервалам  $0010^*$  и 00110; класс  $B_3$  — интервалам  $010^{**}$  и 00111; класс  $B_4$  — интервалу  $011^{**}$ ; класс  $B_5$  — интервалам  $10^{***}$  и  $1100^*$ ; класс  $B_6$  — интервалам  $1101^{**}$ ,  $1110^*$  и 11110. Итак, имеем следующие классы для разбиения  $\Pi_C$ :  $\Pi_1 = \left\{B_2, B_3, B_5, B_6\right\}$  и  $\Pi_2 = \left\{B_1, B_4\right\}$ . Для кодирования классов  $B_i \in \Pi_1$  необходимо  $R_1 = 2$  переменных  $\tau_r \in \left\{\tau\right\}$ .

Однако необходим код, позволяющий идентифицировать тот факт, что  $B_i \not\in \Pi_1$ . В этой связи (в данном примере) разрядность  $R_1$  увеличивается до 3. Пусть код 000 соответствует условию  $B_i \not\in \Pi_1$ . Закодируем классы  $B_i \in \Pi_1$  следующим образом:  $K(B_2) = 001$ ,  $K(B_3) = 010$ ,  $K(B_5) = 100$  и  $K(B_6) = 101$ .

Для формирования таблицы переходов необходимо построить систему обобщенных формул перехода [2,3] для классов  $B_i \in \Pi_C$ . Пусть для классов  $B_1, B_2 \in \Pi_C$  получены следующие формулы:

| $T_1T_2T_3$                   |                   | $\mathbb{B}_2$        |                 |                    |                 |                   |                 |                    |

|-------------------------------|-------------------|-----------------------|-----------------|--------------------|-----------------|-------------------|-----------------|--------------------|

| T <sub>4</sub> T <sub>5</sub> | 000               | 001                   | 010             | 011                | 100             | 101               | 110             | 111                |

| 00                            | [b <sub>1</sub> ] | <b>b</b> <sub>5</sub> | b9              | [b <sub>13</sub> ] | b <sub>17</sub> | b <sub>21</sub>   | b <sub>25</sub> | [b <sub>29</sub> ] |

| 01                            | b <sub>2</sub>    | b <sub>6</sub>        | b <sub>10</sub> | b <sub>14</sub>    | b <sub>18</sub> | b <sub>22</sub> _ | b <sub>26</sub> | b <sub>30</sub>    |

| 10                            | b <sub>3</sub>    | b <sub>7</sub>        | b <sub>11</sub> | b <sub>15</sub>    | b <sub>19</sub> | b <sub>23</sub>   | b <sub>27</sub> | b <sub>31</sub>    |

| 11                            | b4                | (b <sub>8</sub>       | b <sub>12</sub> | b <sub>16</sub>    | b <sub>20</sub> | b <sub>24</sub>   | b <sub>28</sub> | b <sub>32</sub>    |

|                               | $\mathbb{B}_1$    | В                     | 3               | В4                 | В               | s                 | В6              | В7                 |

Рисунок 3 — Адреса микрокоманд КМУУ  $U_5(\Gamma)$

Фрагмент таблицы переходов КМУУ  $U_5(\Gamma)$ , соответствующий (12), приведен в табл.1.

Таблица 1 – Фрагмент таблицы переходов КМУУ U<sub>5</sub>(Г)

| $B_{i}$ | $K(B_i)2$ | $K(B_i)1$ | $b_q$                 | $A(b_q)$ | $X_h$                                                | $\Phi_{h}$  | h |

|---------|-----------|-----------|-----------------------|----------|------------------------------------------------------|-------------|---|

| $B_1$   | 000**     | 000       | <b>b</b> <sub>5</sub> | 00100    | $\mathbf{x}_1$                                       | $D_3$       | 1 |

|         |           |           | $b_8$                 | 00111    | $\overline{\mathbf{x}_1}$                            | $D_3D_4D_5$ | 2 |

| $B_2$   | ****      | 001       | b <sub>17</sub>       | 10000    | x 2                                                  | $D_1$       | 3 |

|         |           |           | $b_8$                 | 00111    | $\overline{\mathbf{x}}_{2}\mathbf{x}_{3}$            | $D_3D_4D_5$ | 4 |

|         |           |           | b <sub>13</sub>       | 01100    | $\overline{\mathbf{x}_{2}}\overline{\mathbf{x}_{3}}$ | $D_2D_3$    | 5 |

В столбце  $K(B_i)$ 1 указан код класса  $B_i \in \Pi_1$ , в столбце  $K(B_i)$ 2 – код класса  $B_i \in \Pi_2$ . Если рассматриваются переходы из класса  $B_i \in \Pi_2$ , то в строке записан код 000. В противном случае, код из столбца  $K(B_i)$ 2 игнорируется.

Таблица переходов служит для формирования функций (11). Например, из табл.1 может быть получена функция

$$D_3 = \overline{T_1} \overline{T_2} \overline{T_3} \overline{\tau_1} \overline{\tau_2} \overline{\tau_3} \vee \overline{\tau_1} \overline{\tau_2} \tau_3 \overline{x_2}.$$

Остальные этапы синтеза выполняются аналогично их описанию в [10]. Только этап 7 имеет некоторые отличия. Рассмотрим следующий пример.

Пусть в вершине  $b_{31}$  ГСА  $\Gamma$  записан набор микроопераций  $y_3, y_7$ . Из

предыдущего материала ясно, что вершина  $b_{31}$  является выходом ОЛЦ  $\alpha_{11}$ , которая входит в класс  $B_6$ . Класс  $B_6$  имеет код  $K(B_6) = 101$ , а вершине  $b_{31}$  соответствует адрес 11110 (рис. 3). Таким образом, в ячейку ЕМВ с адресом 11110 должен быть помещен код набора  $y_3, y_7$  и переменная  $\tau_3$ .

Итак, переменные  $\tau_{\rm r} \in \{\tau^1\}$  помещаются в ячейки УП, соответствующие выходам ОЛЦ, входящим в классы  ${\rm B_i} \in \Pi_1$ . Схема БПА реализуется на LUT элементах. Очевидно, что разбиение множества  $\tau$  на классы  $\tau^1$  и  $\tau^2$  надо производить следующим образом. В класс  $\tau^2$  помещаются переменные  $\tau_{\rm r} \in \{\tau\}$ , которым соответствуют схемы с наименьшим числом LUT элементов. Такой подход позволяет уменьшить аппаратурные затраты в схеме БПА. Дальнейшая реализация схемы КМУУ  ${\rm U}_5$  сводится к реализации системы функций на PLA и УП на ЕМВ. Для решения этой задачи используются стандартные промышленные пакеты [6,7]. Этот этап выходит за пределы нашей статьи.

Отметим, что реализация предложенного подхода возможна только благодаря большому числу входов PLA. Например, в блоках PLA микросхем APEX20K имеется S=32 входа [7]. В общем случае предложенный метод целесообразен при выполнении условия

$$R_1 + R + L \le S. \tag{13}$$

Анализ стандартных примеров [12] показал, что условие (13) выполняется для 87% МПА из этой библиотеки.

#### Выводы

Предлагаемый в работе метод уменьшения аппаратурных затрат в схеме КМУУ основан на учете особенностей гибридных FPGA, а также наличии классов псевдоэквивалентных ОЛЦ. Использование двух источников кодов классов позволяет гарантированно уменьшить число термов в системе функций возбуждения триггеров счетчика адресов микрокоманд до минимально возможной величины. Если КМУУ с общей памятью рассматривать как автомат Мура, то предлагаемый подход позволяет уменьшить число термов до величины этого параметра у эквивалентного автомата Мили. Кроме того, уменьшается число LUТ-элементов в схеме преобразователя адреса, так как не все адреса выходов ОЛЦ подлежат преобразованию.

Кроме того, при выполнении условия (13) схема СФА реализуется в виде одного блока PLA. При этом существенно уменьшается площадь кристалла, занимаемая схемой СФА. Это во многом объясняется уменьшением числа межсоединений по сравнению с КМУУ  $U_1-U_4$ .

*Научная новизна* предложенного метода заключается в использовании особенностей базиса гибридных FPGA (большой

коэффициент объединения по входам блоков PLA) для уменьшения числа LUT элементов в схеме КМУУ.

*Практическая значимость* метода заключается в уменьшении площади кристалла FPGA, занимаемой схемой КМУУ с общей памятью, что позволяет получить схемы, обладающие меньшей стоимостью, чем известные из литературы аналоги.

Дальнейшие направления исследований связаны с разработкой метода синтеза КМУУ, направленного на уменьшение число блоков PLA в схеме адресации при нарушении условия (13).

### Список использованной литературы

- 1. Barkalov A., Titarenko L. Logic synthesis for compositional microprogram control units. Berlin: Springer, 2008. –272 pp.

- 2. Баркалов А.А. Синтез микропрограммных автоматов на заказных и программируемых СБИС / А.А. Баркалов, Л.А. Титаренко. Донецк: УНИТЕХ, 2009. 336 с.

- 3. Barkalov A., Titarenko L. Logic synthesis for FSM-based control units. Berlin: Springer, 2009. –233 pp.

- 4. Maxfield S. The Design Warrior's Guide to FPGAs. Amsterdam: Elsevier, 2004. 541 pp.

- 5. Грушвицкий Р.И. Проектирование систем на микросхемах с программируемой структурой / Р.И. Грушвицкий, А.Х. Мурсаев, Е.П. Угрюмов. С-Пб: БХВ Петербург, 2006.-736 с.

- 6. All Programmable Technologies from Xilinx Inc. [Электронный ресурс] Режим доступа: xilinx.com.

- 7. FPGA CPLD and ASIC from Altera [Электронный ресурс] Режим доступа: altera.com.

- 8. Kaviani F., Brown S. The Hybrid Field Programmable Architecture// IEEE Design & Test of Computers. 1999, V.16, N4. pp. 74-83.

- 9. Sigh S., Singh R., Bhatia V. Performance Evaluation of Hybrid Reconfigurable Computing Architectures over Symmetrical FPGA// International Journal of Embedded Systems and Applications. 2012, V.2, N3. pp. 107-116.

- 10. Оптимизация схемы КМУУ с общей памятью / А.А. Баркалов, Л.А. Титаренко, К.Н. Ефименко, Я.М. Липински // УСиМ. –2011. №5. С. 47-52.

- 11. Разделение схемы адресации в КМУУ с общей памятью / А.А. Баркалов, Л.А. Титаренко, К.Н. Ефименко, И.Я. Зеленёва // Известия ТТИ ЮФУ-ДонНТУ: материалы Четырнадцатого Международного научно-практического семинара [«Практика и перспективы развития партнерства в сфере высшей школы»]: в 3-х кн. Таганрог: ТТИ ЮФУ, 2013. Кн. 2. №13 С. 11-16.

- 12. Yang S. Logic synthesis and optimization bench marks user guide. Technical report. Microelectronic Center of North Carolina, 1991. 44pp.

Надійшла до редакції 07.09.2013

Рецензент: канд. техн. наук, доц. Приходько Т.О.

- 42 -

О.О. Баркалов<sup>1,2</sup>, Л.О. Титаренко<sup>1</sup>, К.М. Єфіменко<sup>2</sup>, І.Я. Зеленьова<sup>2</sup>

Університет Зеленогурьський (Польща)<sup>1</sup>,

Донецький національний технічний університет<sup>2</sup>

Реалізація КМУУ із загальною пам'яттю на гібридних FPGA. Пропонується метод зменшення апаратурних витрат в схемі КМПК із загальною пам'яттю, який орієнтовано на технологію гібридних FPGA. Метод засновано на використанні двох джерел кодів класів псевдоеквівалентних ОЛЛ та реалізації схеми адресації мікрокоманд на вбудованих PLA. Такий підхід дозволяє зменшити загальну площу кристала, яку займає схема пристрою керування. Наведено приклад використання запропонованого методу. Ключові слова: КМПК, алгоритм керування, операторний лінійний ланцюг, гібридні FPGA, логічна схема.

**A.A. Barkalov<sup>1,2</sup>, L.A. Titarenko<sup>1</sup>, K.N. Efimenko<sup>2</sup>, I.J. Zelenjova<sup>2</sup>** University of Zielona góra (Poland)<sup>1</sup>, Donetsk National Technical University (Ukraine)<sup>2</sup>

**Implementation of CMCU with common memory in hybrid FPGA.** The proposed method is bound for reducing the hardware amount of scheme compositional microprogramming control unit (CMCU) with shared memory, oriented to the technology of hybrid FPGA. The method is based on the using of the hybrid FPGA structural features. This method is effective if there are certain classes of pseudoequivalent operational linear chains (OLC) in the original control algorithm.

In this paper we propose a method for the synthesis of compositional microprogramming control unit, including the steps: forming a plurality of operational linear chains on a given graph diagram of the control algorithm; the formation of classes pseudoequivalent OLC; coding these classes; optimal addressing of microinstruction in classes using a modified Karnaugh map; forming the table of CMCU transitions; forming a truth table for the block of address transforming; forming the table of control memory contents; implementation of the compositional microprogramming control unit scheme in a given element basis.

As a result of application of the proposed approach to encoding (addressing) of the microinstructions the address of each microinstruction in control memory is formed from two parts, i.e. as concatenation of address of the pseudoequivalent OLC class and local address of the microinstruction inside of this OLC. Using two sources of codes classes allows guaranteed to reduce the number of terms in the trigger excitation functions of the counter of microinstructions addresses to the minimal possible value. The control memory of CMCU can be implemented on the reconfigurable embedded memory blocks (EMB). The combinational circuit of address generation is implemented on the embedded programmable logic arrays (PLA). If CMCU with shared memory is viewed as a Moore automaton, the proposed approach reduces the number of terms to the value of this parameter in the equivalent Mealy automaton. In addition, the number LUT elements in the circuit of address converter is reduced because not all output addresses of the OLC must be transformed.

Under the certain conditions this method also allows to implement the scheme of addresses as a single unit PLA. This significantly reduces the chip area occupied by the circuit.

An example of application of the proposed method is considered. The steps of appropriate modification of the basic structure CMCU are detailed. Further researches of authors are focused on finding of approach to reduce the number of used PLA blocks embedded in the scheme of formation microinstruction address.

Keywords: CMCU, control algorithm, operational linear chain, hybrid FPGA, PLA, logic circuit.